The tool used by Synopsys to do power analysis is: Primetime PX Prime PTPX iron can analyze the PrimeTIme track for power estimation after logic synthesis, so we only need to use the PrimeTIme PX for power analysis. enough.

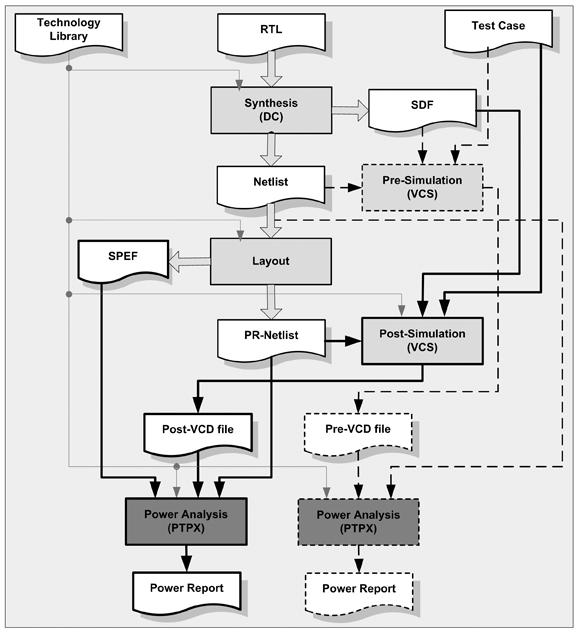

The figure above shows the flow of power analysis after placement and routing and logic synthesis.

one. Logical synthesis power analysis

The documents used are: 1. Logical synthesis of Verilog files

2. Constraint file used in static timing analysis

3. RTL simulation files, I use the VCD, after all, the standard each simulator supports ~

4. There is a library file for power consumption information. Decibels, this library file can report cells in a library to see if there are any.

With these files, you can do power analysis. Here's the power analysis process:

1. Allow power analysis feature set power_enable_analysis

2. Set the factors for the analysis mode setting.

3. Read in design and library files

4. Specified working conditions

5. Timing Analysis update_TIming

6. Get activity data

If it is an RTL-level netlist file, use RTL to tell the PT that the specified VCD file was before placement and routing. If the VCD is a zero_delay emulation, that is, a purely functional emulation, the home zero_delay option, if all specified, is a gate-level default.

7. Set power analysis options set_power_analysis_opTIons:

-static_leakage_only option The set_power_analysis_options command only supports average power analysis mode.

-waveform_interval-cycle_accurate_cycle_count, -cycle_accurate_clock, -waveform_format, - waveform_output, including -include_groups option only supports time-based power analysis mode.

8. Power Analysis update_power

9. Generate power report report_power

To illustrate, PTPX is an enhanced feature of primetime, using only one PT script, and I took my own pt script and shared it out:

File:pt.tcl

###########################################

# Set power analysis mode

###########################################

Set true power_enable_analysis;

Set average power_analysis_mode;

###########################################

# Read and gate level netlist link

###########################################

Set SEARCH_PATH ". / Source DB / / Results"

Set link_library "typical.db"

Set target_library "typical.db"

Read_verilog jnd_90s.v

Set top_name JND

Current_design JND

link

###########################################

# Read SDC and transition time or annotation parasitism

###########################################

Read_sdc pt_con.tcl

###########################################

# Check, update or report timing

###########################################

Check_timing

Update_timing

Report_timing

###########################################

# read switch activity file

###########################################

read_vcd-RTL test platform jnd_all.vcd strip_path

Report_switching_activity list_not_annotated

###########################################

# Check or update or report power

###########################################

Check_power

Update_power

Report_power level

two. Post-layout power analysisPower format. Not introduced here.

#Read library, design, make power analysis

# and link design

Set to power_enable_analysis true

Set link_library slow_pgpin.db

Read_verilog power_pins.v

link

# Create backup power network

Create_power_net_info vdd_backup power

Create_power_net_info vss_backup-GND

# Create a domain power grid

Create_power_net_info t_vdd Power Switch

-nominal_voltages {1.2} voltage_ranges {1.1 1.3}

Create_power_net_info a_vdd power

Create_power_net_info b_vdd power

# Create a domain ground network

Create_power_net_info t_vss-GND

Create_power_net_info a_vss-GND

Create_power_net_info b_vss-GND

# Create an internal power network

Create_power_net_info int_vdd_1 Power

-nominal_voltages {1.2} voltage_ranges [1.1 1.3}

Switchable

Create_power_net_info int_vdd_2 power

-nominal_voltages {1.25} voltage_ranges {1.1 1.3}

Create_power_net_info int_vdd_3 power

-nominal_voltages {1.2} voltage_ranges {1.1 1.3}

Create_power_net_info int_vdd_4 power

# Create a power domain

One create_power_domain ton

a create_power_domain pair object_list [get_cells PD0_inst]

POWER_DOWN power_down_ctrl [A] get_nets

Power_down_ctrl_sense 0

a create_power_domain B_object_list get_cells PD1_inst]

POWER_DOWN

# Rails connected to the power domain

Connect_power_domain T-primary_power_net t_vdd

Primary_ground_net t_vss

Connect_power_domain a_vdd of a primary_power_net

-primary_ground_net a_vss

-backup_power_net vdd_backup

Backup_ground_net vss_backup

Connect_power_domain B-primary_power_net b_vdd

Primary_ground_net b_vss

# Set the voltage of the power grid

Set_voltage 1.15 object_list {t_vdd a_vdd b_vdd}

# Read SDC and other time or power assertions

Set_input_transition 0.0395 [all_inputs]

1.0 set_load [All Output]

#carried out. Timing analysis

Update_timing

#Read switch activity

Set_switching_activity . .

Set_switching_activity . .

. . .

Report_power

three. About the reportA standard report:

Power Group Power Supply Power Supply (%)ATTRS

-------------------------------------------------- -------------

Io_pad 0.0000 0.0000 0.0000 0.0000 (0.00%)

Memory 0.0000 0.0000 0.0000 0.0000 (0.00%)

Black_box 0.0000 0.0000 0.0000 0.0000 (0.00%)

Clock_network 0.0000 0.0000 0.0000 0.0000 (0.00%)

Registration 8.442e-05 1.114e-05 9.208e-09 9.557e-05 (29.97%) I

Combination 0.0000 0.0000 0.0000 0.0000 (0.00%)

Order 0.0000 0.0000 0.0000 0.0000 (0.00%)

Attributes

----------

- Including drive register power

Internal switch leakage clock

Power Supply Power Supply (%)ATTRS

-------------------------------------------------- -------------

CLK 1.813e-04 4.199e-05 4.129e-10 2.233e-04

-------------------------------------------------- -------------

Expected Clock1.813e 04 4.199e 054.129e 102.233e-04 (70.03%)

Switching power net = 5.313e-05 (16.66%)

Cell internal power = 2.657e-04 (83.33%)

Battery leakage power = 9.627e-09 (0.00%)

---------

Total power = 3.188e-04 (100.00%)

Report on the gated clock:

Report_clock_gate_savings

****************************************

Report: Clock Gate Savings

Power_mode: average

Design: mydesign

Version: D-2009.12

Date: October 29, 2010 12:08:20 2009

****************************************

-------------------------------------------------- ----------------

Clock: CLK

+ Clock switching rate: 0.392157

+ Number of registers: 19262

+ Number of clocks: 12

+ Average clock switching rate in register: 0.305872

+ Average switched savings register: 22.0%

-------------------------------------------------- ----------------

Switch savings number %

Distribution register register

-------------------------------------------------- ----------------

100%0 0.0%

80% - 100%76 0.4%

60% - 80% 5660 29.4%

40% - 60%0 0.0%

20% - 40%8 0.0%

0% - 20%0 0.0%

0%13518 70.2%

----------------------

Whether the game can be played smoothly depends on the low latency of the projector, whether it can be optimized to within 30ms, or within 50ms, which is difficult for non-professionals to perceive. However, the cable and network speed and the configuration of the computer (game console) have an impact on the game delay, so you can't completely throw the pot to the display device.

The first is the problem of memory. Be sure to choose a larger one, the bigger the better, otherwise the screen will freeze. The second is that the resolution must be above 1080p, otherwise the details of the projected game screen will not be clear, which will greatly affect the game experience and viewing experience. The other is about motion compensation. The game screen is generally faster for animation playback. It must be equipped with motion compensation, otherwise the screen will be stuck.

gaming projector,gaming mini projector,gaming projector best buy,4k gaming projector hdmi 2.1,best gaming mini projector

Shenzhen Happybate Trading Co.,LTD , https://www.happybateprojector.com