Introduction In systems such as video surveillance and remote video playback, video graphics data is typically transmitted over the network to a remote processor. As a dedicated processor for digital signal processing, DSP has great advantages in video compression, etc., but it is difficult to implement functions such as task management and network communication. The Linux operating system running on the general-purpose embedded processor, open source, can modify the kernel as needed, support various network protocols, and its task scheduling mechanism has excellent performance. Combining the advantages of both, the embedded video platform can complete the graphics processing function by the DSP, and transmit the video data to the embedded microprocessor through the high-speed interface, and then the network transmission function is completed by the embedded Linux system.

At present, the high-speed communication methods between DSP and microprocessor are as follows: shared memory, this technology has very high design requirements for software and hardware, and the same efficiency is also the highest; general high-speed bus interface, such as PCI, USB, etc. Various types of communication methods use complex link protocols, software design is difficult; dedicated interfaces, such as HPI (Host Port Inter-face) provided by TI DSP. This paper studies the HPI interface of TMS320E)M642, and proposes a software and hardware implementation scheme for high-speed communication between TMS320DM642 and AT91RM9200. Through the HPI interface, the TMS320DM642 can transmit real-time video data to the AT91RM9200 at high speed. On the AT91RM9200, the Lnux driver implements memory-mapped I/O and physical memory remapping, avoiding secondary copying of video data between the application and the kernel. Improve the network delivery efficiency of the application.

This article refers to the address: http://

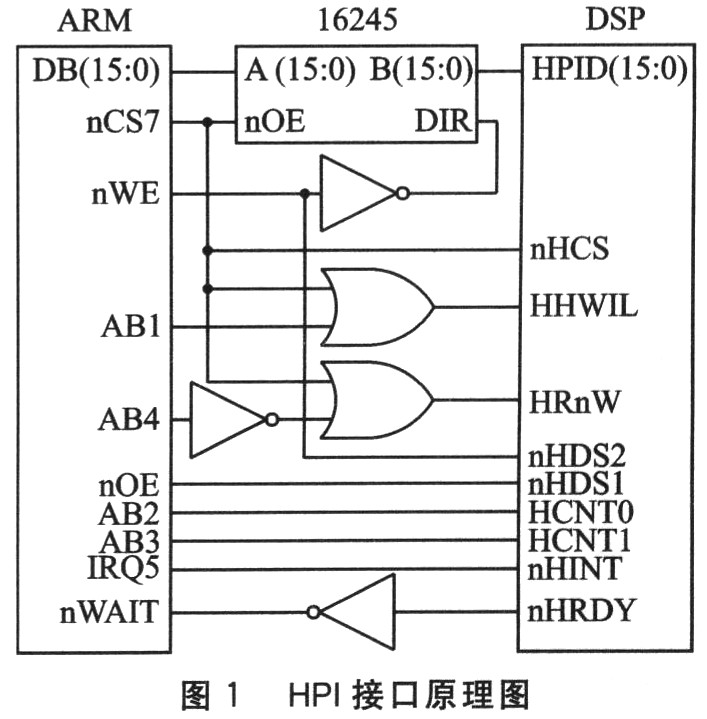

1 HPI interface hardware design HPI is a parallel interface, supporting 32-bit (HPl32) and 16-bit (HPll6) data bus, through the HPI data registers (HPIDA, HlPIDF), ARM can indirectly access the DSP storage space. Inside the DSP, the transfer of data from the memory location to the HPI data register is done by the EDMA (Enhanced DMA) controller.

The peripheral pins of the HPI controller include HD[0-31] and data bus. HCNTL[O-1] is the register access control line. The HPI controller has four registers. Through these two control lines, the DSP can determine the register that ARM needs to access. Among them, HPIA address register, store the address of the current access unit; HPIC is the control register to implement various control commands; HPIDA self-growth data register, each time the content of this register HPIA is added 4; HPIDF fixed address data register, different from HPIDA The point is that the contents of HPIA remain unchanged after accessing this register. HHWIL, high and low access control line, it is only used in HPll6 mode, this control pin determines whether the upper or lower 16 bits of the register are accessed by the host. HR/nW, read and write control line of 4 registers of HPI controller. HDSl, HDS2 and HCS, HDS1, HDS2 can be connected to the ARM read and write control lines, HCS is connected to ARM's nCS7 chip select line, the three are combined in the DSP to form a HSTROBE signal, when the HCS is low effective and HDSl or HDS2 read Or write low is valid, determine the read or write operation of the data register (HPIDA, HPIDF). HAS, address latch line, when the host's address line is multiplexed with the data line, the host can use the control line to notify. DSP latch address; other times when the control line is not used, it should be connected to a high level. nHRDY, DSP output line, indicating whether the HPI bus is accessible. nHINT, interrupt output line, used to interrupt ARM.

The DSP and ARM interface circuit is shown in Figure 1. In HPI16 mode, 16 data lines are connected to the lower 16 bits of the ARM data bus through the 16245 data isolator, and the HPI chip select space is placed on the ARM nCS7 chip select line. The HR/nW read/write signals are connected via the inverter. To the ARM's AB4 address line, HCNTL[O-1] is connected to the ARM's address line AB[2-3]. The read base address of the four registers of the HPI is 0x80000000, and the write base address is 0x80000010. Access from these two addresses on the ARM side, access to the HPI 4 registers accordingly.

ARM reads and writes the DSP data space through HPI, and must be executed in the following three steps: First, the HPIC register is initialized, mainly for the lowest bit HWOB bit setting of HPI16 mode, and the data transmission format is determined by the upper half word (set to 0). , or the lower half of the word first (set to 1), this bit is invalid for HPI32 mode, can not be set; then, initialize the HPIA register, set the address of the access unit; finally read the data through the read and write data registers (HPIDA, HPIDF) Write operation, in which the read and write HPIDA register is to complete the continuous address unit read and write operations, read and write HPIDF register is to complete the fixed address unit read and write operations. Note that in the ARM read and write process, if the DSP's nHRDY control line is always high, indicating that the HPI data bus is not ready, the ARM read and write operations must wait; when nHRDY is low, the ARM continues to execute instructions downward.

2 Linux driver design Although Linux is a monolithic operating system, it allows dynamic loading or deletion of functional modules at runtime. This feature facilitates the development of the driver function module. The Linux system supports two module calling methods: one is static compilation, compiled directly into the kernel, and runs when the system starts; the other is dynamic loading. When the kernel is running, insmod/rmmod is used to implement module loading and deleting. . In the development of embedded systems, dynamic loading is generally adopted to avoid frequent system restarts. When the product is finally released, the module can be compiled directly into the kernel. This treatment is relatively simple and efficient.

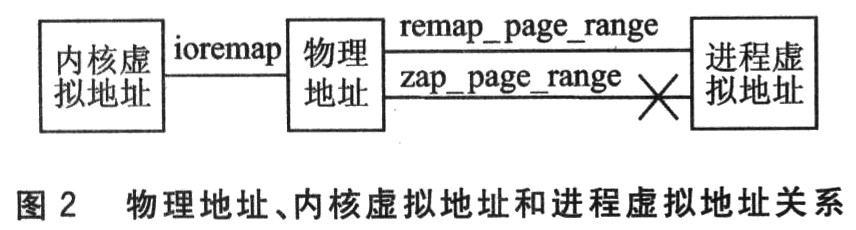

In Linux systems, memory addresses mainly involve the following concepts: physical address, kernel virtual address (including kernel logical address), and process virtual address. At the kernel level, when the kernel wants to access a memory space, the kernel virtual address is used, and the MMU (memory management unit) converts the kernel virtual address to a physical address. With virtual memory technology, each process has a virtual space that does not interfere with each other. The relationship between the three direct mapping is shown in Figure 2, in which the kernel function zap_page_range completes the function of removing the mapping relationship between the physical address and the process virtual address.

2.1 Driver Structure In Linux, devices are also accessed as files. VFS (Virtual File System) provides a unified access interface for a variety of different file systems, through which applications can access and control devices directly using system calls such as open, read, and IOctl.

In this example, the HPI is used as a peripheral device, and its driver mainly implements functions such as opening, closing, memory mapping, video data buffer management, and physical memory switching. According to the schematic diagram, the physical address corresponding to the four registers of the HPI can be determined. In the driver initialization process, the ioremap_uncache function is called to map the physical address to the kernel virtual address, and the driver layer accesses the four registers of the HPI through the kernel virtual address.

The memory mapped I/O maps the data space allocated by the HPI driver directly to the virtual address space of the application, and the application directly accesses the space, avoiding the secondary copy of the video data caused by the read/write system call. In the kernel, a certain cache is allocated by the driver. When the application cannot process the video data sent by the DSP in time, the data can be cached; when the application processes one frame of image, the physical memory switching technology of Linux is used to put the next The physical address where the frame data is located is remapped to the same virtual address of the application, so that the application does not need to frequently call the mmap function to map memory.

2.2 Memory Mapped I/O

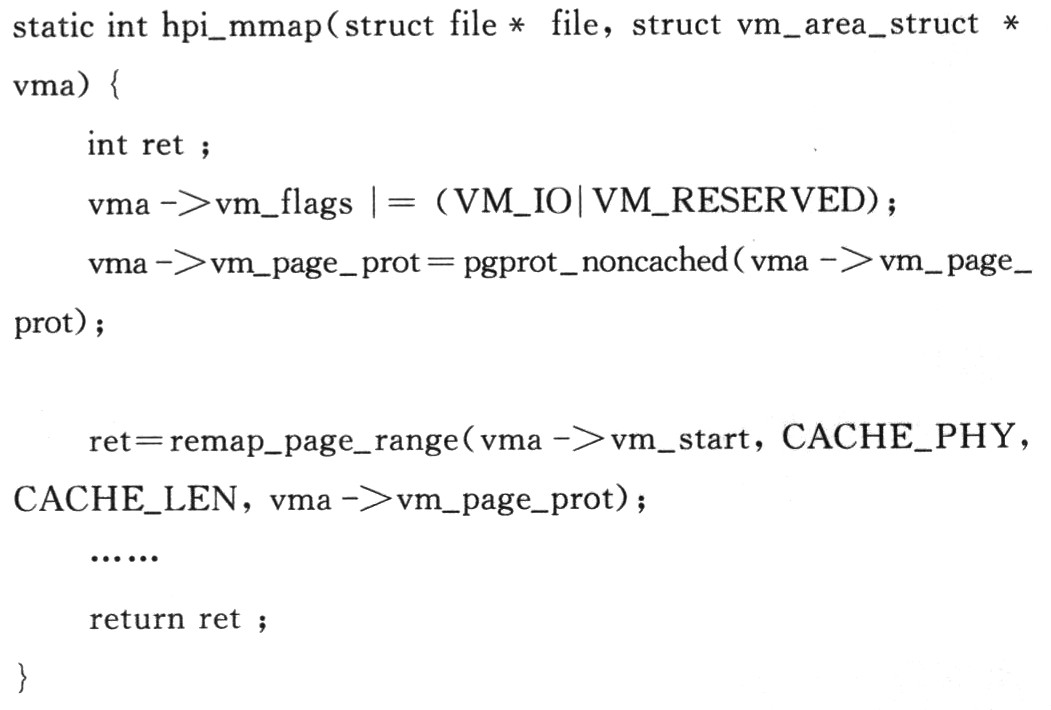

In general, when an application reads or writes device data with read/write, the device driver first samples the device data from the device to the kernel buffer, and then copies it from the kernel buffer to the application buffer. The data passes through two. Secondary copy. When the amount of data is small, such as some control commands or status information, there is almost no impact on system performance. However, if the amount of data transmitted at one time is relatively large, such as real-time video images on a video card, two copies will greatly affect the data processing efficiency of the system. At this time, memory mapped I/O technology can be used, and the memory layer mapping I/O in the kernel layer is completed by the function remap_page_range.

As can be seen from the prototype of the remap_page_range function, the significance of this function is that by mapping a specific physical address to a process virtual address, the process can access a specific physical address, which is not possible under normal circumstances. In this example, when the process calls the mmap function for memory mapping, the kernel calls the hpi_mmap function that is registered by the driver. One of the parameters passed in includes the process virtual address. In the hpi_mmap function, remap_page_range is called to complete the mapping from the physical address of the buffer to the virtual address of the process. The hpi_mmap function is implemented as follows:

The vm_flags field sets VM_RESERVED, indicating that the data buffer is always resident in memory and will not be swapped out when there is insufficient memory. The kernel and the process read and write to the data buffer at the same time. In order to ensure data consistency, access to the area should not pass through the internal buffer of the CPU, so use pgprot_noncached to set the unbuffered flag.

The mmap system call returns a process virtual address, which is the vma->vm_start field. The process accesses the virtual address and eventually becomes access to the physical address CACHE_PHY.

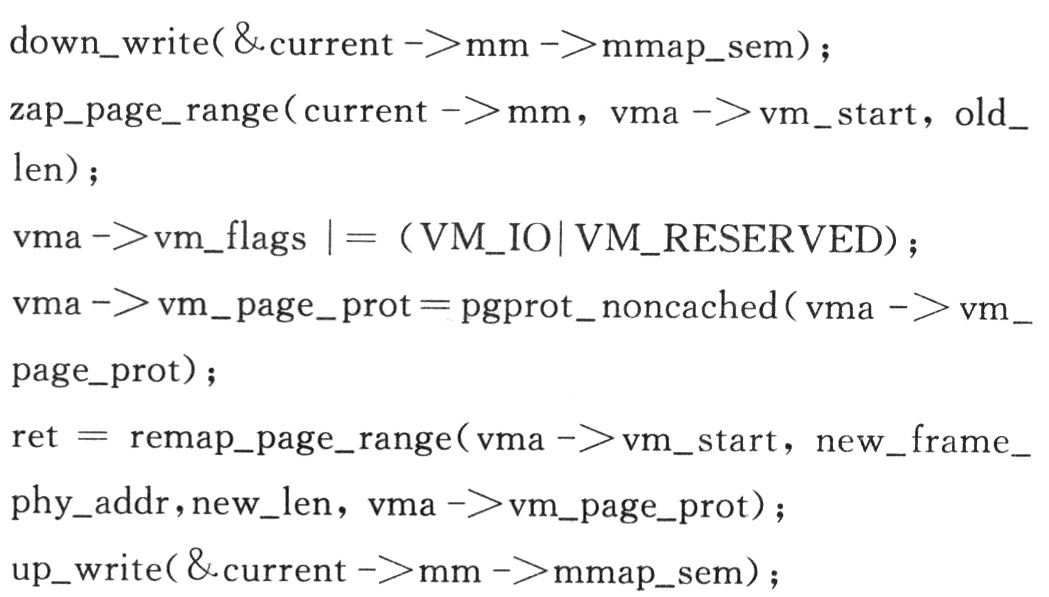

2.3 Data Buffer Management The main task of buffer management is to assign a corresponding cache to the ARM when it receives a new frame and remap the physical address to the process virtual address. When the application processes the frame, the buffer management is responsible for the recycling of the memory area.

When the Linux kernel starts, you can pass the parameter mem=PHY_LEN to specify the size of the storage space. In this example, 8 MB of high-end physical memory is reserved for the HPI driver when the kernel boots. In this example, with the idea of ​​managing ordinary peripheral I/O memory (PCI card memory, etc.) in Linux, a continuous area is represented by a tree of height 2. The advantage of this data structure is that the resource allocation is simple, and the algorithm complexity of merging discrete small memories into one continuous large buffer is O(1). For specific implementation, please refer to the relevant part of the resource structure in the kernel source code.

Re-mapping a new frame of video data to a process virtual address is another task of buffer management. Because the physical address of the previous frame has been mapped to the process virtual address, the mapping relationship between the physical address of the previous frame and the process virtual address is removed, and then the current frame data is remapped to the process virtual address. The mapping between the physical address and the process virtual address is completed by the kernel function zap_page_range. After the function is called, if the process accesses the virtual address again, the kernel will generate a page fault interrupt. At this time, remap_page_range is used to establish the mapping relationship between the current frame data physical address and the process virtual address, and the process can access the current frame data through the same virtual address. The significance of this method is that the process does not need to frequently call mmap to establish the mapping between physical address and virtual address. It only needs to be called once. When new data arrives, the driver automatically maps the new frame data to the previous process virtual address, which improves the process processing. The efficiency of video data. The implementation code is as follows:

Conclusion On the current video processing platform, video processing, video transmission, and complex task management are generally performed by a single DSP processor. The technical solution that works in conjunction with other embedded microprocessors has just started. After testing, on the video processing platform designed based on the high-speed communication method proposed in this paper, the communication speed between TMS320DM642 and AT9lRM9200 can reach 50 Mbps, and the bandwidth is enough to transmit compressed video data such as MPEG. If you use HPl32 mode, the speed will be greatly improved. At the same time, because the real-time nature of the Linux system is not very strong, if other real-time operating systems, such as Vxworks, are used, the system performance will be greatly improved.

(1) Large screen temperature indication with heating indicator light, working status at a glance.

(2) Microcomputer control, heating and insulation automatic control.

(3) The inner liner is made of high-quality steel plate and equipped with a liner protection device, which is anti-corrosion and pressure-resistant and durable.

(4) It has multiple safety protection functions such as leakage protection, anti-dry protection, over-temperature protection, over-pressure protection, and leakage warning.

(5) The insulation layer is foamed with thickened polyurethane, which has good heat preservation effect and saves energy.

(6) It has a wide range of water pressure and large capacity, and can be used for water at the same time.

Solar Pv Water Heater,Solar Water Heater,No Need Electricity Solar Water Heater,Pv Water Heater

Jinan Xinyuhua Energy Technology Co.,Ltd , https://www.xyhenergy.com