Digital Signal Processing (DSP) is an emerging discipline that covers many disciplines and is widely used in many fields. Since the 1960s, with the rapid development of computer and information technology, digital signal processing technology has emerged and developed rapidly. In the past two decades, digital signal processing has been widely used in the field of communications and other DSP technology diagrams. Digital signal processing uses a computer or a dedicated processing device to collect, transform, filter, estimate, enhance, compress, and recognize signals in digital form to obtain a signal form that meets people's needs.

This article brings you a DSP chip based audio signal filtering system design solution sharing.

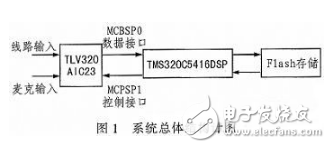

Hardware designThe system uses DSP chip TMS320C5416 and TLV320AIC23 audio codec chip to realize the software and hardware design of the system, and on this basis, the voice signal acquisition, playback, storage and analysis functions are completed. The text includes three parts: audio signal acquisition, DSP chip processing signal, flash memory. The overall design structure of the system is shown in Figure 1.

TMS320C5416 is the main chip used in the text. It is a low-power, high-performance DSP chip. Its main functions include collecting voice signals, storing and controlling communication between modules. The audio signals are collected and compressed and stored in the flash memory. Does the AIC23's high-performance stereo signal input support MIC and LINE? IN two ways, configurable register selection, and programmable gain adjustment. Its internal integrated analog-to-digital and digital-to-analog conversion components use advanced sampling technology with a sampling range of 8K to 96K.

The design of the slave chip TLV320AIC23 audio codec chip is a stereo audio Codec chip, which is mainly responsible for A/D conversion, sampling and encoding and filtering of voice signals. The chip is an ideal audio analog device with wide application; three DSP chips There are two buffer serial ports MCBSP0 and MCBSP1 which are responsible for controlling the audio chip AIC23. The MCBSP0 serial port is the SPI interface to realize the transmission and reception of voice data. The MCBSP1 serial port is the I2S interface, the task is to write the control word; the Flash memory module can quickly access the erasable wiper. Write, even if the power failure information will not lose the data memory, and the cost is low, high reliability, strong stability, large capacity of several GB, small size and other characteristics, read and store operations as a carrier.

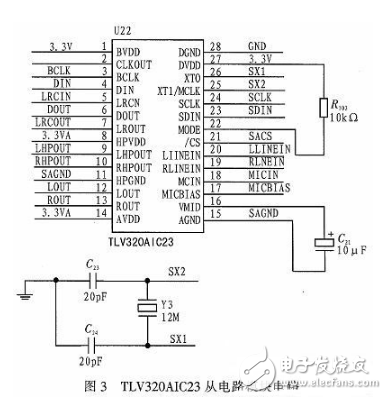

System hardware circuit designThe DSP chip TMS320C5416 used in this system has a maximum frequency of up to 160 MIPS, and the system has good real-time performance; the audio codec chip TLV320AIC23 has a sampling accuracy of 16 to 32 bits. The combination of the above two chips is an ideal design for solving the mobile audio recording and playback system and collecting voice in the field. The three MCBSPs of the TMS320C5416 can easily implement control and communication between AIC23. AIC23 is a programmable chip, which contains 11 16-bit registers. The MODE pin selects whether the control interface uses SPI or I2C. MODE=0 uses I2C mode; MODE=1 means SPI mode.

The AIC23 independent control port receives the controller's command word, while the independent data interface exchanges DSP voice data. The working clock for the DSP is a 12M external crystal. The MCBSP0 of the C5416DSP of this system is connected to the control interface of AIC23, and the MCBS P1 is connected to the data interface of AIC23. The interface block diagram of TMS320C5416DSP connected to TLV320AIC23 is shown in Figure 2.

This design uses TMS320C5416 chip, its internal 128K*16 RAM, can effectively improve the system integration and overall performance. In addition, it has 3 multi-channel buffer serial ports, providing 128 channels. The C5416 chip features: operating frequency up to 160 MIPS; accessible data storage space 64K, I / O space 64K.

The TMS320C5416 and TLV320AIC23 are connected as follows: BCLKX0/1: Transmit clock signal, which is the serial shift clock signal of the multi-channel buffer serial interface transmitter. When reset, the default is input. When OFF is low, BCLKX enters high configuration; when TMS320C5416 is connected to FLASH device, DSP chip collects 32 bits of voice data each time, and then writes to Flash device from left channel to right channel for storage.

TLV320AIC23 voice acquisition and playback interface circuit moduleThe AIC23 integrates an ADC and DAC internally, is compatible with the C5416's input/output voltage, and its digital interface is seamlessly connected to the DSP's MCBSP port. AIC23 uses advanced Sigma-delta oversampling technology to transfer most of the noise to the resistive state. The sampling frequency range is 8K to 96K. It provides four kinds of 16-bit, 20-bit, 24-bit and 32-bit sampling data, and the output of ADC and DAC. The signal to noise ratio is 90 dB and 100 dB, respectively.

The pin diagram of the TLV320AIC23 connected to the TMS320C5416 is as follows. BCLK: I2S digital audio interface clock signal, serial data transmission clock. When the main mode is AIC23, BCLK is generated by AIC23 and transmitted to DSP by this frequency. At this time, the frequency is only 1/4 of the main clock. When in slave mode, DSP generates BCLK; DIN: I2S format input to D/A converter; DOUT, stereo ADC generation, I2S format A/D converter serial data output: LRCIN/LRCOUT: I2SD/A and A/D converter word clock signal In the master mode, AIC23 generates this signal and sends it to the DSP. In slave mode, it is generated by the DSP; SCLK: control port serial clock input; SDIN: control port serial data input, control protocol, transmission configuration data; /CS: In SPI mode, it is the data latch control terminal, in I2C mode, as the last bit of the peripheral 7-bit address; XTI/MCLK: external clock input. In this paper, AIC23 is provided by an external crystal oscillator, and the TLV320AIC23 is derived from the circuit module circuit as shown in Figure 3.

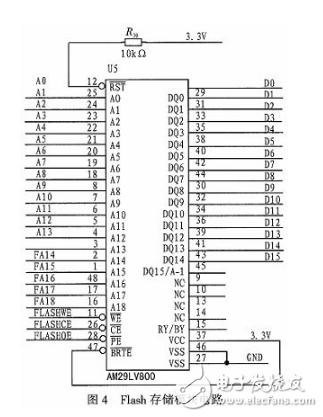

The voice data storage module of this paper adopts 32M*8-bit Flash memory space, which can satisfy the capacity of the memory chip and the speed of reading voice signals. The recording and playback system data is stored in the flash memory. Flash consists of a set of 1KB blocks that can be erased independently. Erasing a block will reset the block to all ones. The base address of each block of the flash memory is fixed. The flash memory is in the starting position in memory, typically starting at zero. Figure 4 below is a circuit diagram of the flash memory module.

Flash memory is a kind of non-volatile memory, and its storage characteristics are equivalent to hard disks. Therefore, it becomes a storage medium for portable digital devices. At the same time, Flash memory adopts a serial structure. The read/write unit is in units of pages and blocks, and the capacity can be large and the cost is low. And can ensure the correctness of data reading and writing. The I/O port of the flash memory has 8 bits, and the data transmission method is to transmit the command word in turn. The 32-bit voice data collected by the DSP is divided into four times through the external bus, and is written into the flash memory from left to right.

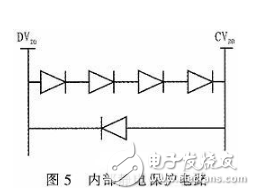

Power interface moduleThe power supply structure of the TMS320C5416DSP uses a dual-supply device chip, a core power supply CVDD and an I/O power supply DVDD, which need to consider the relative voltage and power-on sequence. The two power supply control strategies are different: DVDD is a single 3.3 V power supply, while CVDD only loads 1.6 V. Lowering the power supply is to reduce the power consumption of the chip. Dual power mode eliminates delays between power supplies. Ideally, the I/O power supply and the core power supply should be powered up at the same time, but it is not easy to do it in practice. If it is not possible to power up at the same time, it is necessary to configure the operating mode according to the pin level. The core should be given priority over the I/O power supply, requiring one voltage to be lower than the operating voltage and the other voltage not to exceed the required power supply time. During power-up, ensure that the I/O buffer receives the correct core output and prevents system bus collisions. The power-on sequence mainly depends on the internal electrostatic protection circuit as shown in Figure 5.

As can be seen, the DVDD does not exceed CVDD 2 V, so four diodes are used to step down, and the core power supply cannot exceed the I/O supply voltage by 0.5 V. Therefore, only one diode is used, otherwise the chip is easily damaged.

System software design moduleThe software environment of this voice recording and playback system is the DSP integrated development environment IDE provides mature core functions and convenient graphical visualization tools, making the design faster. CCS2.0 adopts graphical interface interface, editing tools and project management tools, providing software development, program debugging and simulation environment, integrating assembler, compiler, and database building tools. The CCS integrated code debugging tool has various debugging functions, and supports assembly and C/C++ languages. The program software of this system is written in C language. It is easy to debug, and can improve the execution efficiency of the software. It can perform command level simulation and real-time data analysis on the DSP. It also has a rich library function.

The software part of the system is mainly collected from the field line input and the microphone voice, collected and stored in the flash memory, filtered and broadcasted, and the signal is transformed into the frequency domain, that is, FFT discrete Fourier fast transform.

Speech analysis submoduleThe voice signal input on the scene is sent to the stereo audio codec AIC23. The AIC23 controls the on-chip registers, converts the signal A/D, processes the digital signal with a digital computer, and then filters it by the digital filter and sends it to the flash memory for temporary storage. The digital filter is a discrete time system. Program speech module processing: First initialize the system, including setting the clock generator, AIC23 initialization, multi-channel buffering, initial work variables, and so on.

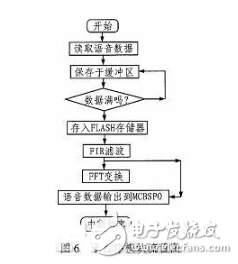

Speech analysis program module processing: TLN320AIC23 initialization, voice recording data is stored in the data buffer after reading, call FIR digital filter filtering, the effect is outstanding, then the digital voice signal is temporarily stored in the flash memory, and finally issued by the earphone, while performing FFT Discrete fast transform algorithm. Voice data is output to the MCBSP. The flow analysis subroutine module flow chart is shown in Figure 6.

Using the finite length of the window function, a windowed linear phase FIR digital filter can be implemented to meet the common problems of transfer sequences or impulse responses.

b=fir1(n,Wn,'ftype');

b=fr1(n,Wn,'ftype','window');

n is the order of the filter, Wn is the cutoff frequency, ftype determines the filter type, high is the high-pass filter, and stop is the band-stop filter. Window adopts the window function type, which is a design method that makes the infinite long non-causal sequence become the finite-length pulse response sequence by truncation and weighting. The default value is Hamming window, w=hamming(n), which is generated. An n-point Hamming window function. Write the matlab program, generate the FIR coefficient stored in FH[n], and display the result in the display area after the program runs.

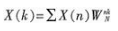

FFT is an efficient method for quickly calculating DFT, which can significantly reduce the amount of computation and greatly improve the speed of DFT. Most DSP chips can perform multiply-accumulate operations in a single instruction cycle. The FFT algorithm uses the characteristics of DFT coefficients, combining operations to convert long sequences into short sequence DFTs to reduce the amount of computation. The implementation process of the FFT algorithm:

1) Decompose the time domain signal of the N point into N time domain signals, form a signal at a single point, and calculate the spectrum.

2) Bit inversion of the input data, that is, the input sequence is sorted into the order in which the bit order is reversed. Bit code inversion can improve program execution speed and storage efficiency.

3) Implement N-point complex FFT, perform 3 loop sets to calculate FFT transform, and perform butterfly operation on the innermost layer. The first stage, the second stage, the third stage and the log2N level are butterfly operations. An FFT algorithm in which the number of sequence points is N=2m and N is an integer power of two.

4) Estimated power

X(k) is generally divided into an imaginary part and a real part, and the data transformed by the FFT algorithm is squared in the calculation.

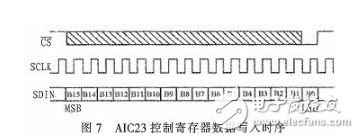

Control register programmingThe TLV320AIC23 in this paper utilizes serial transmission of data. The first half of the data control stores the register address, and the second half stores the value to be written in the register. Control data for serial transmission using two 8-bit processing. In combination with the actual text, the assembly language is used for the I2C write module.

The DSP sends the configuration command to the AIC23 through the I2C bus, completes the initial configuration, and then the AIC23 starts working. The initialization of AIC23 is recorded in an array, and the command is sent by the serial port and sent in a round-robin manner. The AIC23 data write timing diagram is shown in Figure 7.

As shown in the figure, B[15~9] is the address of the recording control register, and B[8~0] is the value to be written and is stored in the register.

Pcb Fan,Bldc Fan Pcb,Pcb Cooling Fan,Fan Regulator Pcb

Full Industrial CO.,ltd. , https://www.iotaindustrial.com